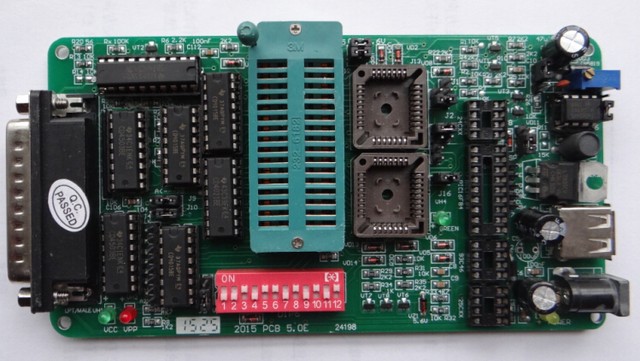

Data input mode, CE low, read data, CE high.Data (address Lo), OE 0, (and left 0 for now), Address low now into EPROM, U1 feeding Lo into EPROM, U2 feeding Hi into EPROM.Data (data 0-7), CE low, PRG 0.1 (held low for programming time).

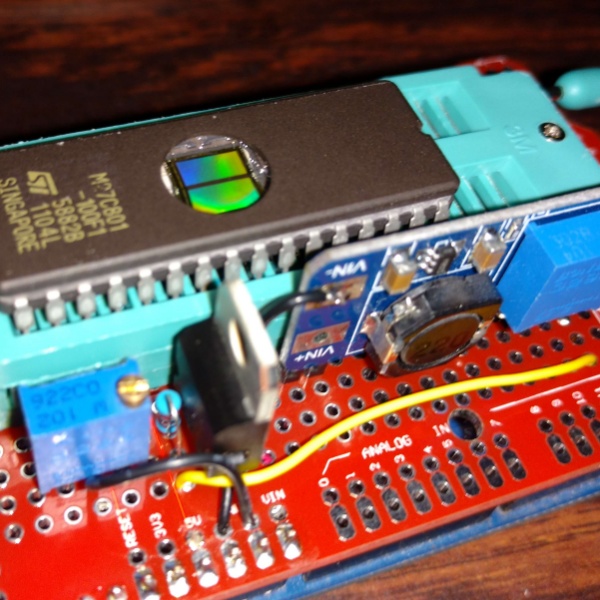

Data (address Lo), OE 0-1, Address low now into EPROM, U1 feeding Lo into EPROM, U2 feeding Hi into EPROM.Data (address Hi), OE 0-1, Address high now U1 -> U2, EPROM ignored signals as CE high.Just getting my head round this (mostly for my own clarification as I have a project to do something similar but its very deep down my to-do list!) Saves a control pin at the expense of slightly more code complexity (Woz style!) I did wonder about that myself - so it's a 2 deep, 8-bit wide shift register. Setting up the address requires writing the hi address byte followed by the lo address byte to the latch ICs. The latch chips copy data on the inputs to the outputs on the rising edge of the CP input signal. Don’t you need two separate control signals to clock different address data into the 74HC574 flip-flops?

0 Comments

Leave a Reply. |

AuthorWrite something about yourself. No need to be fancy, just an overview. ArchivesCategories |

RSS Feed

RSS Feed